Â

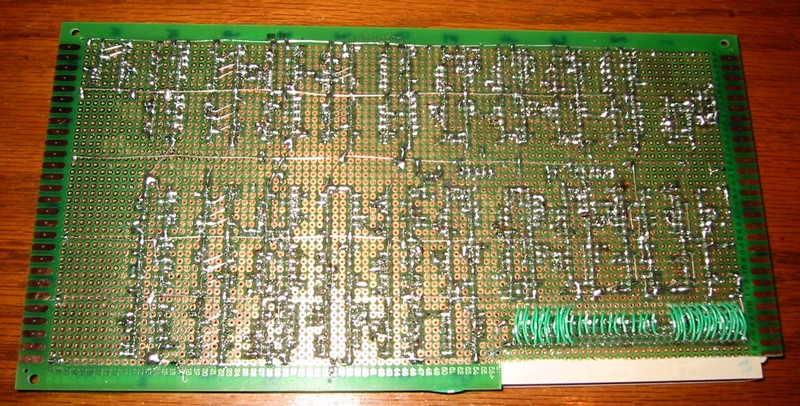

NAND Gates are very versatile. You might remember back in the TTL days when you were out of a specific chip you could always grab a NAND chip out of the bin and re-purpose it to work. This NANDputer looks like it would be a bit harder to troubleshoot than the one that I am using to write this on!

“While the CPU architecture is fairly conventional, the way it is implemented isn’t. I went with a bit-serial setup on here to save gates. The ALU for example is only 1 bit, with a “latching†carry so operations are performed a bit at a time on the 8 bit registers/memory. The program counter is also bit-serial, and on the first youtube video you can see the carry propagating during the incrementing of it.

The downside of course is that this is much slower than a parallel architecture, but this way takes vastly fewer gates. It takes 96 clock cycles to run a single instruction: There’s 16 “T†states and 3 non-overlapping clocks generated using a 6 stage johnson counter with some NAND decoding.  (The flipflops that form the johnson counter are made from NANDs too). Thus, it’s 16*9 or 96 cycles per instruction. The clock runs at 10MHz, so this is a bit over 100KIPs (thousands of instructions per second). This sounds really slow but it isn’t TOO slow. It’s faster than a TMS1000, and it’s only 2-3x slower than a Commodore 64 which I estimate at 250-300kips when it runs at 1MHz (3 and 4 cycle instructions being some of the more common ones).”